SIMLES

SIMLES یک نشانه ایرانی است که به تولید دستگاه های الکترونیک و عمدتا بی سیم می پردازد.ما راه های کنترل تجهیزات آسانی را برای شما فراهم میکنیم.

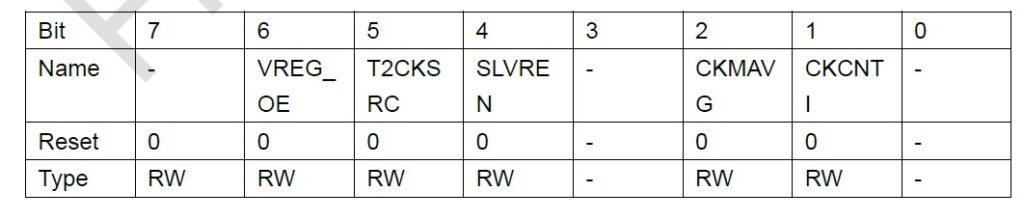

BIT6 : Regulator output enable

0 = PA4 and PC5 are normal IO

1 = On-chip regulator is turned on, PA4 and PC5 output regulator voltage

BIT5 : TIMER2 clock source selectio

0 = TIMER2 clock source is the system clock

1 = TIMER2 clock source is internal 32MHz

BIT4 : SLVREN

Software controlled LVR enable bits, when UCFG1<1:0> are ’01’:

1 = Turn on LVR

0 = disable LVR

when

When UCFG1<1:0> is not 01, this bit has no practical meaning

Note: This bit will not be cleared when a Brown-out Reset occurs

0 . Any other reset will reset it

clear 0

BIT3 : Reserved bit, cannot write 1

BIT 2 : CKMAVG

Fast clock measurement slow clock period measurement averaging mode

1 = Turn on averaging mode (automatically measure and accumulate 4 times)

0 = Turn off averaging mode

BIT1 : CKCNTI

Clock Count Init

Enable fast clock to measure slow clock period

1 = Enable fast clock to measure slow clock period

0 = Disable fast clock to measure slow clock period

Note: This digit will automatically return to zero after the measurement is completed

BIT0 : Reserved bit, cannot write 1

SIMLES یک نشانه ایرانی است که به تولید دستگاه های الکترونیک و عمدتا بی سیم می پردازد.ما راه های کنترل تجهیزات آسانی را برای شما فراهم میکنیم.

کليه حقوق اين سایت برای SIMLES محفوظ می باشد.

Copyright © 2020-2025 Simles.ir

تعطیلات

از پنج شنبه 18/بهمن/1403 تا روز شنبه 27/بهمن/1403 فروشگاه تعطیل می باشد.کلیه سفارشات در این تاریخ از یکشنبه 28 بهمن ماه به مرور ارسال می گردد.

خرید در این بازه با تخفیف 8 درصدی و از طریق کد تخفیف SD

آخرین دیدگاهها